### THE PROLIFERATION OF HETEROGENEOUS INTEGRATION APPROACHES IN SILICON (NITRIDE) INTEGRATED PHOTONICS

**Roel Baets**

SPIE Photonics West 2020

### ACKNOWLEDGEMENTS

#### Photonics Research Group

professors P. Bienstman, W. Bogaerts, S. Clemmen, B. Kuyken, G. Morthier,

G. Roelkens, N. Le Thomas, D. Van Thourhout

many postdocs and PhD's

GHENT

UNIVERSIT

IMEC CMOS process line

and ePIXfab www.epixfab.eu

#### Funding and collaborations through national and EU research projects

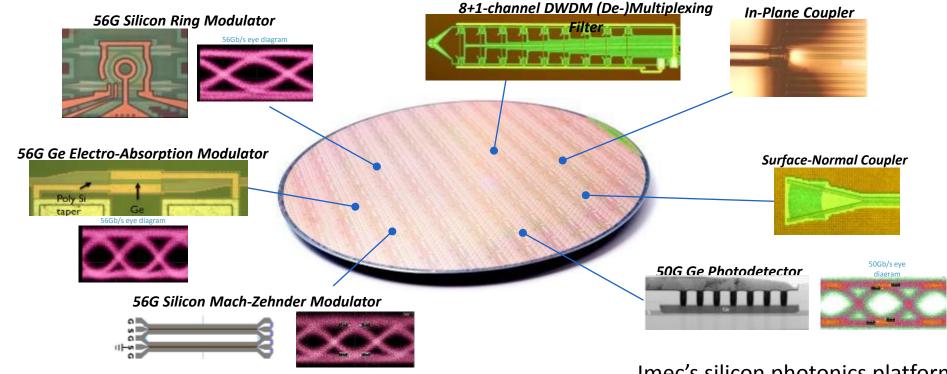

### SILICON PHOTONICS PLATFORMS TODAY

GHENT

UNIVERSITY

unec

Today's mature silicon photonics manufacturing platforms are <u>"homogeneous" or</u> <u>"monolithic"</u>: they build on materials and processes that are well established in CMOS environments.

#### OUTLINE

The need for heterogeneous integration

Diversity in heterogeneous integration

Moving to wafer-scale heterogeneous process flows

The case of III-V on silicon

#### LIMITATIONS OF CURRENT SOL AND SIN (OPEN ACCESS) PIC PLATFORMS

| Feature/function                 | SOI                                  | SiN               |

|----------------------------------|--------------------------------------|-------------------|

| Light source integration         | Not established                      | Not established   |

| Phase modulation<br>(electronic) | Spurious AM<br>Bandwidth limitations | Not established   |

| Phase modulation<br>(thermal)    | Power hungry                         | Very power hungry |

| Linear waveguide loss            | Good, not superb                     | Superb            |

| Nonlinear waveguide loss         | Problematic at high<br>power         | Superb            |

| Integrated detectors             | Good                                 | Not established   |

| Integration with<br>electronics  | Limited options                      | Not established   |

|                                  |                                      |                   |

### WHAT IS HETEROGENEOUS INTEGRATION

#### **Generic:**

# **Heterogeneous Integration** refers to the **integration** of separately manufactured components into a higher level assembly that, in the aggregate, provides enhanced functionality and improved operating characteristics

#### In silicon photonics:

Heterogeneous Integration refers to the wafer-level integration of separately manufactured components or CMOS-uncommon materials onto silicon photonics wafers that, in the aggregate, provides enhanced functionality and improved operating characteristics

#### FUTURE SOLAND SIN (OPEN ACCESS) HETEROGENEOUS PIC PLATFORMS

| Feature/function                 | SOI              | SiN    |

|----------------------------------|------------------|--------|

| Light source integration         | Superb           | Superb |

| Phase modulation<br>(electronic) | Superb           | Superb |

| Phase modulation<br>(thermal)    | Superb           | Superb |

| Linear waveguide loss            | Superb           | Superb |

| Nonlinear waveguide loss         | Less problematic | Superb |

| Integrated detectors             | Superb           | Superb |

| Integration with<br>electronics  | Superb           | Superb |

|                                  |                  |        |

#### OUTLINE

The need for heterogeneous integration

Diversity in heterogeneous integration

Moving to wafer-scale heterogeneous process flows

The case of III-V on silicon

HETEROGENEOUS INTEGRATION: A STORY OF MANY MATERIALS

**III-V** on silicon

- Colloidal quantum dots on silicon

- Liquid crystals on silicon

- Electro-optic materials on silicon (LiNbO<sub>3</sub>, BTO, PZT, polymers, ...)

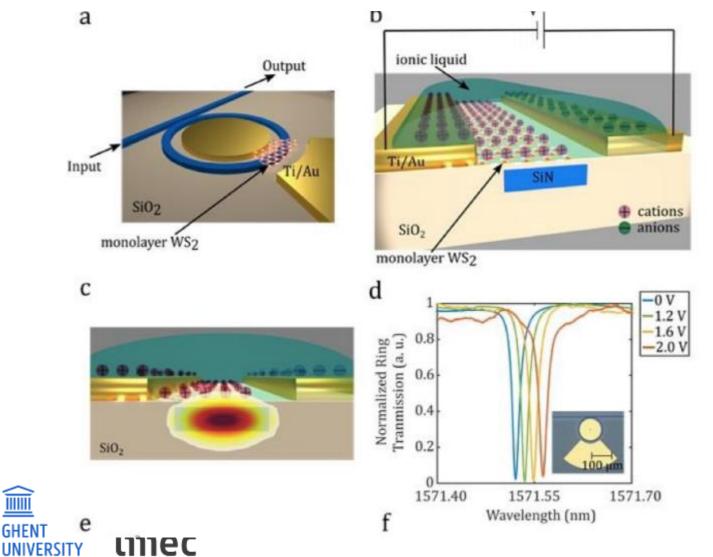

- 2D-materials (graphene, WSe<sub>2</sub>, WS<sub>2</sub>, MoS<sub>2</sub>...)

Etc.

### FIGURES OF MERIT FOR A PHASE MODULATOR

Modulation efficiency  $V_{\pi}L_{\pi}$

Voltage swing

Modulation bandwidth

Optical bandwidth

Size

$\widehat{\blacksquare}$

**Optical insertion losses**

Spurious intensity modulation

**Power dissipation**

mec

**CMOS** compatibility

SOI carrier depletion/injection modulators are good enough for many applications but fail to serve others

Exploration of many alternatives, based on heterogeneous integration of electro-optic materials with SOI or SiN Organic materials Lithium Niobate BTO (Barium Titanate) PZT (Lead Zirconate Titanate)

Emergence of waveguide-MEMS based approaches

### HETEROGENEOUS MODULATOR TECHNOLOGIES

Phase modulators:

**GHEN1**

unec

- LiNbO<sub>3</sub>: thin films bonded on silicon (nitride) circuitry (Harvard, Stanford, Sun Yat-sen University, UCSD, Sandia, UCSB…)

- BTO (Barium Titanate): epitaxially grown on silicon with STO buffer layer (IBM, Yale, imec, ...)

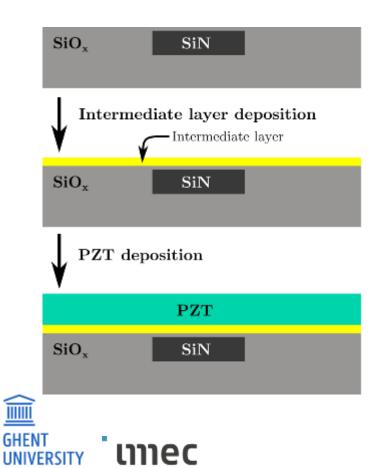

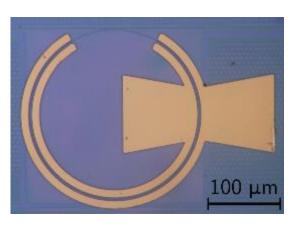

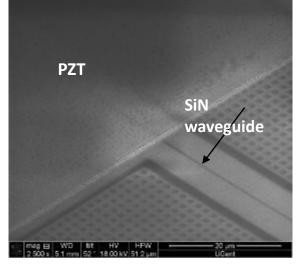

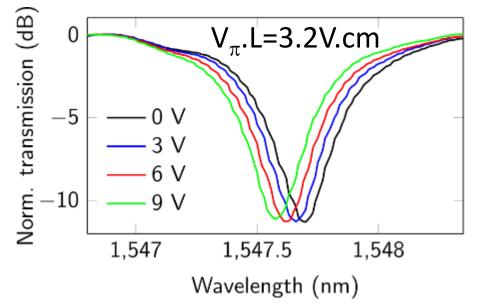

- PZT: sol-gel deposition on any substrate (Ghent University)

- EO-polymers: (KIT, ETHZ...)

Amplitude/phase modulators:

- Graphene: layer transfer (Berkeley, CNIT, imec ...)

- 2D TMDCs (Columbia University, George Washington University...)

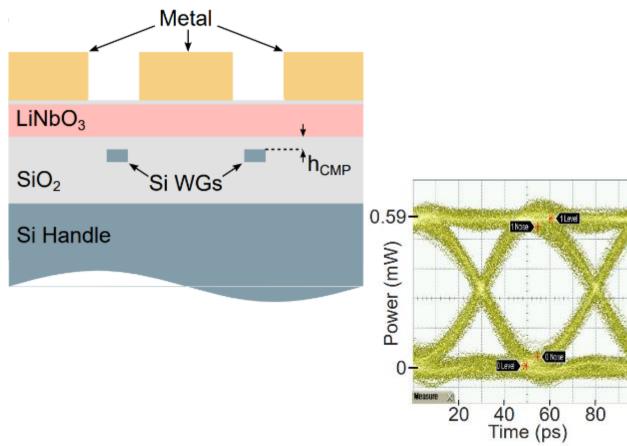

### LITHIUM NIOBATE ON SI HETEROGENEOUS INTEGRATION

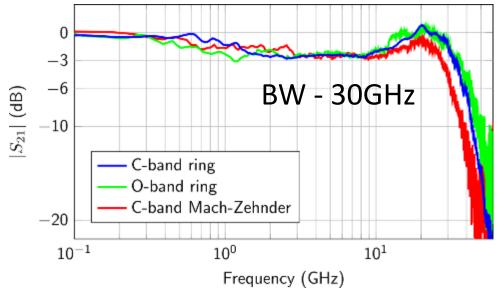

P. O. Weigel, *et. al.*, "Bonded thin film lithium niobate modulator on a silicon photonics platform exceeding 100 GHz 3-dB electrical modulation bandwidth," Opt. Express **26**(18), 23728–23739 (2018).

$\widehat{\blacksquare}$

GHENT

UNIVERSITY

ເກາec

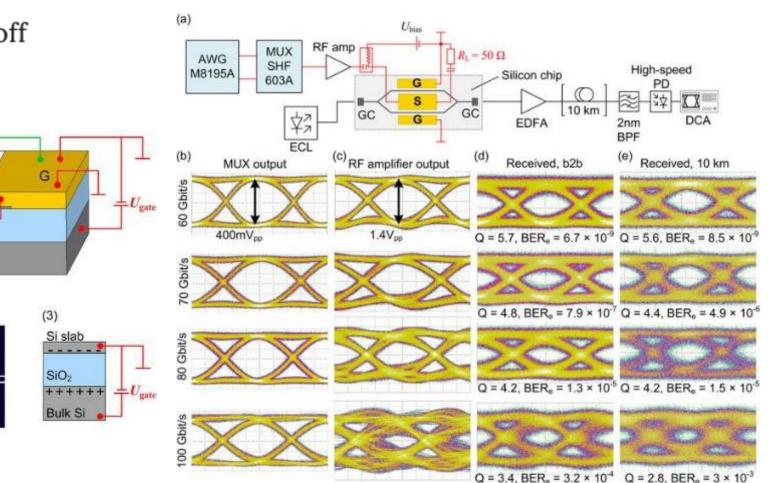

100 Gb s<sup>-1</sup> OOK

He, M., *et. al.*, "High-performance hybrid silicon and lithium niobate Mach-Zehnder modulators for 100 Gbit s<sup>-1</sup> and beyond," Nat. Photonics **13**, 359–364 (2019). https://doi.org/10.1038/s41566-019-0378-6

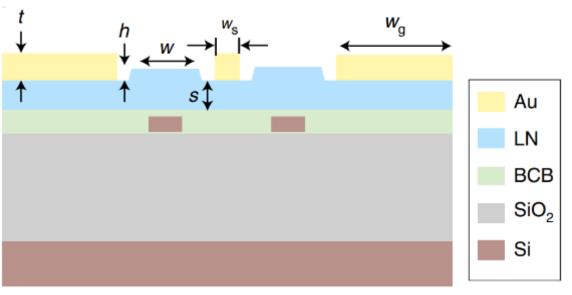

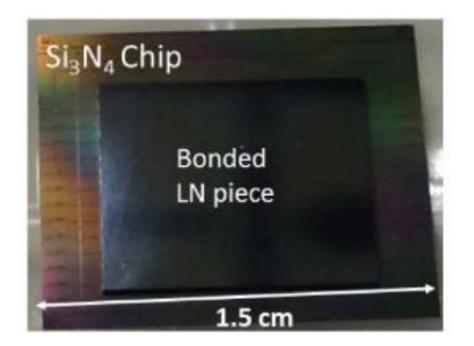

### LITHIUM NIOBATE ON SIN HETEROGENEOUS INTEGRATION

L. Chang, *et. al.*, "Heterogeneous integration of lithium niobate and silicon nitride waveguides for wafer-scale photonic integrated circuits on silicon," Opt. Lett. 42, 803-806 (2017).

GHENT

UNIVERSITY

unec

N. Boynton, *et. al.*, "A heterogeneously integrated silicon photonic/lithium niobate travelling wave electro-optic modulator," Opt. Express 28, 1868-1884 (2020).

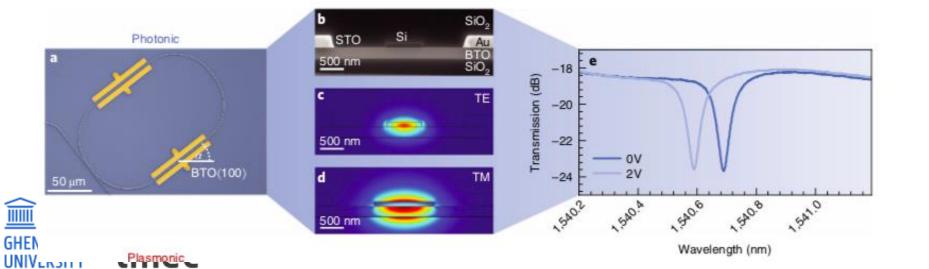

#### Large Pockels effect in micro- and nanostructured barium titanate integrated on silicon

Height BTO MO BTO SO, SI SO, SI BTO MO BT

mature

#### Stefan Abel, et al, Nature Materials (2019)

Epitaxy on Silicon wafer Bonding on SiO2 a-Si waveguides

$V_{\pi}$ .L=0.45V.cm 50GBit/s in plasmon slot waveguide

## Nanophotonic Pockels modulators on a silicon nitride platform

Koen Alexander et al, Nature Communications (2018)

#### SCIENTIFIC REPORTS

Article OPEN Published: 03 April 2018

4

MMI

Out 4

(a)

(c)

Transmission [dB]

#### Silicon-Organic Hybrid (SOH) Mach-Zehnder Modulators for 100 Gbit/s on-off Keying

G

Si slab

Opt.  $\underline{\mathcal{E}}_{0,x}$  field

SiO<sub>2</sub>

Silicon

(1)

EO polymer

(1)(2)

Si rail

R

hslab

(3)

RF Ex,RF field

Wslot

**№** Udrive

(2)

(b)

#### $V_{\pi}$ L=0.09 V.cm, allows very high speed modulators with low drive voltage

Stefan Wolf et al, <u>Scientific Reports</u> (2018) 18

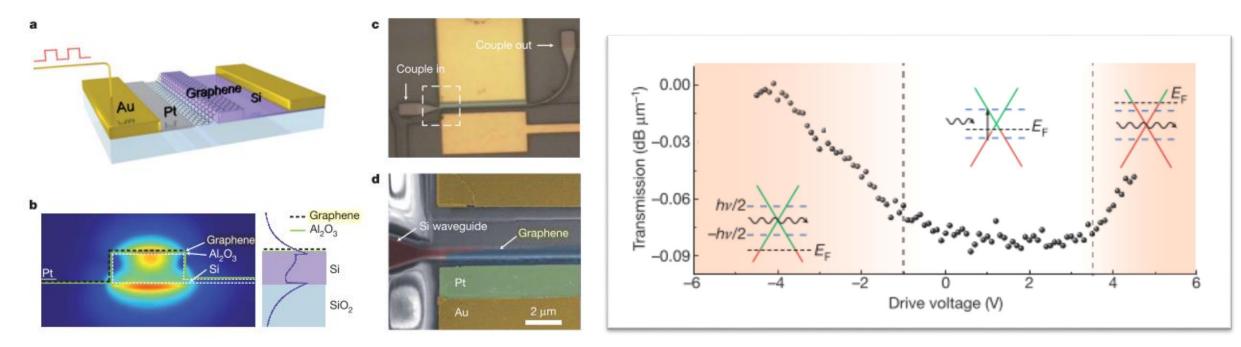

#### A graphene-based broadband optical modulator

Ming Liu<sup>1</sup>\*, Xiaobo Yin<sup>1</sup>\*, Erick Ulin-Avila<sup>1</sup>, Baisong Geng<sup>2</sup>, Thomas Zentgraf<sup>1</sup>, Long Ju<sup>2</sup>, Feng Wang<sup>2,3</sup> & Xiang Zhang<sup>1,3</sup>

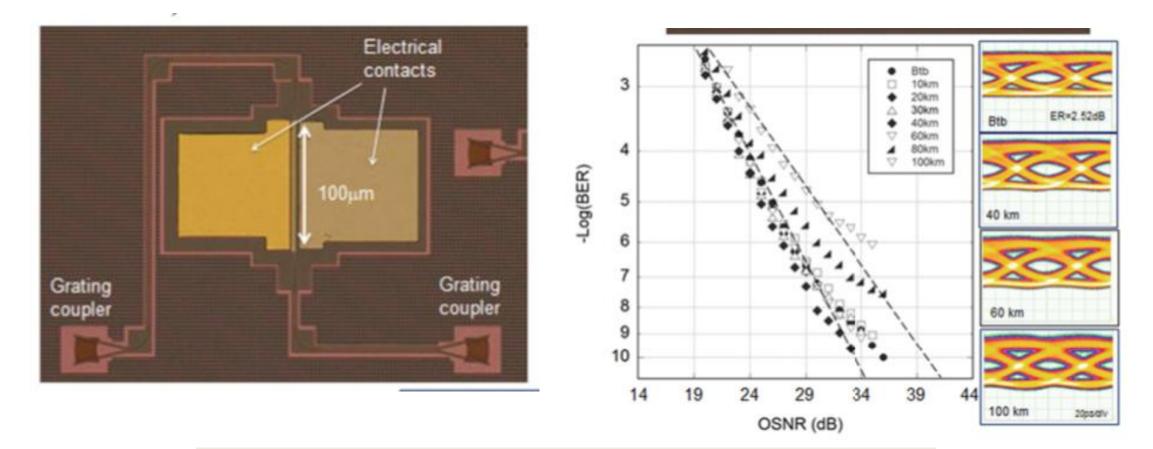

Current demonstrations up to 50GBit/s (eye diagrams), by CNIT & IMEC

#### **GRAPHENE MODULATORS**

20

GHENT UNIVERSITY

unec

First Demonstration 50GBit/s modulation with graphene modulators (CNIT)

20

#### Low-loss composite photonic platform based on 2D semiconductor monolayers

Authors: Ipshita Datta, Sang Hoon Chae, Gaurang R. Bhatt, Mohammad A. Tadayon, Baichang Li, Yiling Yu, Chibeom Park, Jiwoong Park, Linyou Cao, D. N. Basov, James Hone, Michal Lipson

**GHEN1**

- Strong phase-modulation observed in several 2D-materials

- Very low amplitude modulation

- Based on carrier injection: speed?

See also Sorger-group (several arxiv papers)

#### OUTLINE

The need for heterogeneous integration

Diversity in heterogeneous integration

Moving to wafer-scale heterogeneous process flows

The case of III-V on silicon

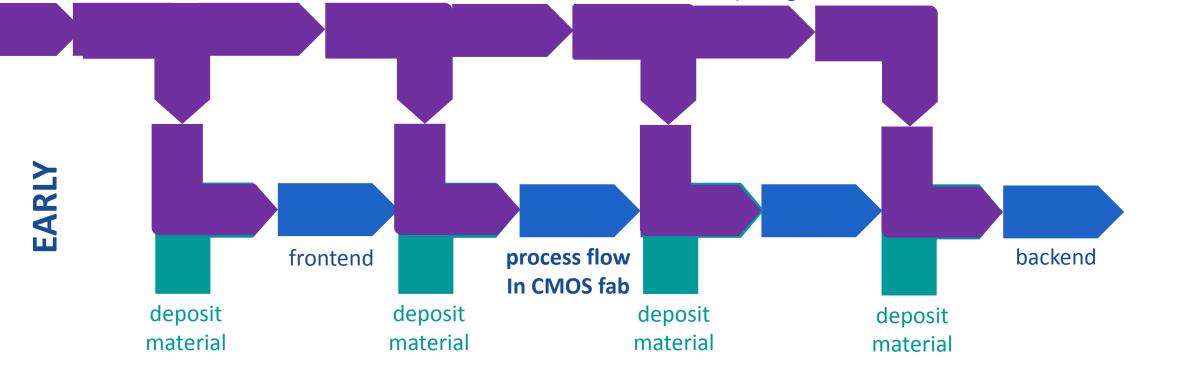

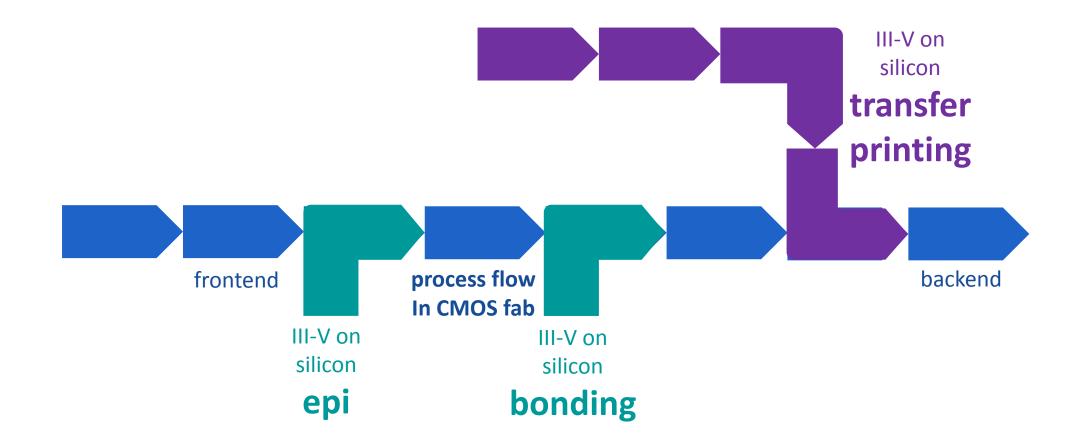

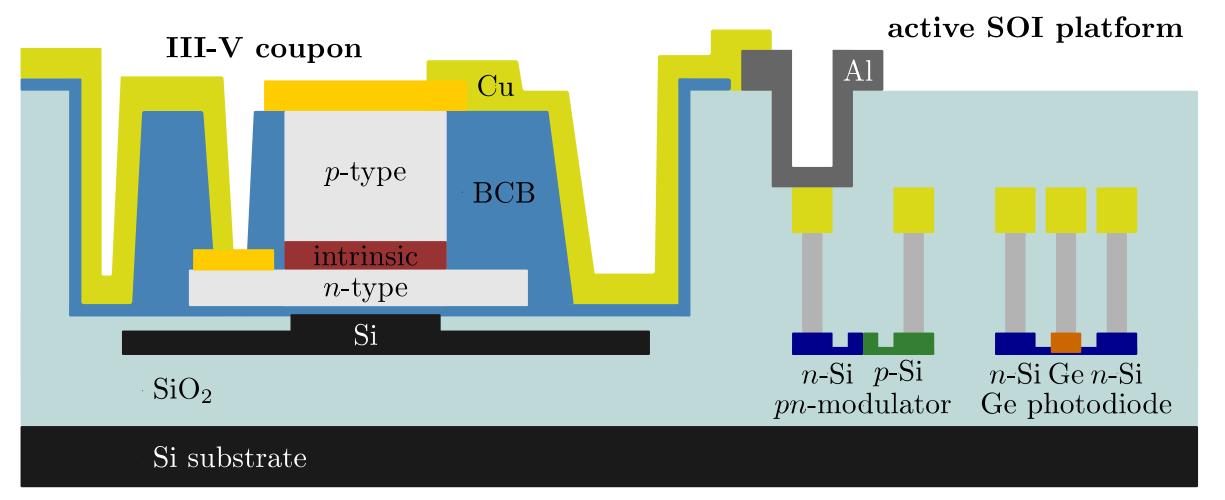

### MOVING TO WAFER-SCALE HETEROGENEOUS PROCESS FLOWS

Challenges:

- Thermal budget

- Annealing steps for heterogeneous material may damage earlier processing

- Annealing steps needed in later processing may damage heterogeneous material

- Contamination

- Heterogeneous material may contaminate process tools (eg gold)

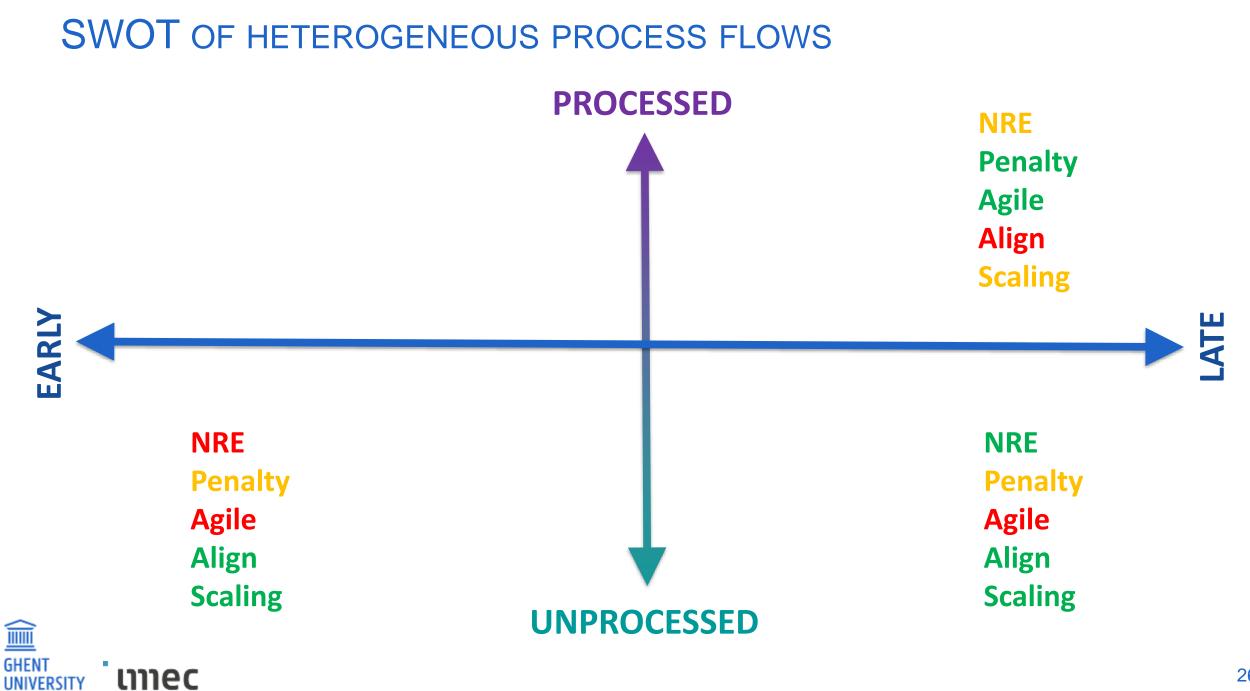

### **DIVERSITY IN HETEROGENEOUS PROCESS FLOWS**

process wafer or chiple<sup>1</sup>/<sub>3</sub> process wafer or chiple<sup>1</sup>/<sub>9</sub> process wafer or chiple<sup>1</sup>/<sub>5</sub> process wafer or chiplets

Integrate on Si wafer 2) Integrate on Si wafer 2) Integrate on Si wafer 2) Integrate on Si wafer

**UNPROCESSED**

#### **DECISION FACTORS**

lmec

Non-recurrent engineering and tool investment cost NRE Heterogeneous integration leads to penalties in performance Penalty Technology serves many heterogeneous integration cases and Agile enables fast routes to market Heterogeneous integration requires precise alignment Align Scaling to high volume manufacturing with low cost Scaling

UNIVERSITY

#### OUTLINE

The need for heterogeneous integration

Diversity in heterogeneous integration

Moving to wafer-scale heterogeneous process flows

The case of III-V on silicon

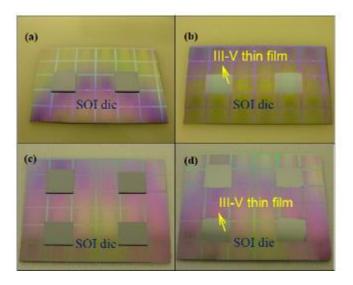

### WAFER-LEVEL APPROACHES FOR III-V INTEGRATION ON SI PICS

#### die-to-wafer bonding

GHENT

UNIVERSITY

umec

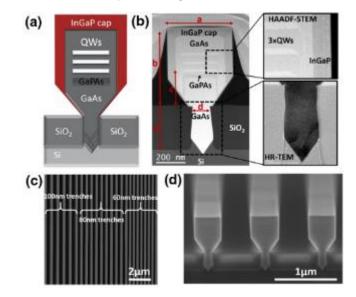

#### **III-V** epitaxy on silicon

#### micro transfer printing

### **III-V ON SILICON TECHNOLOGIES**

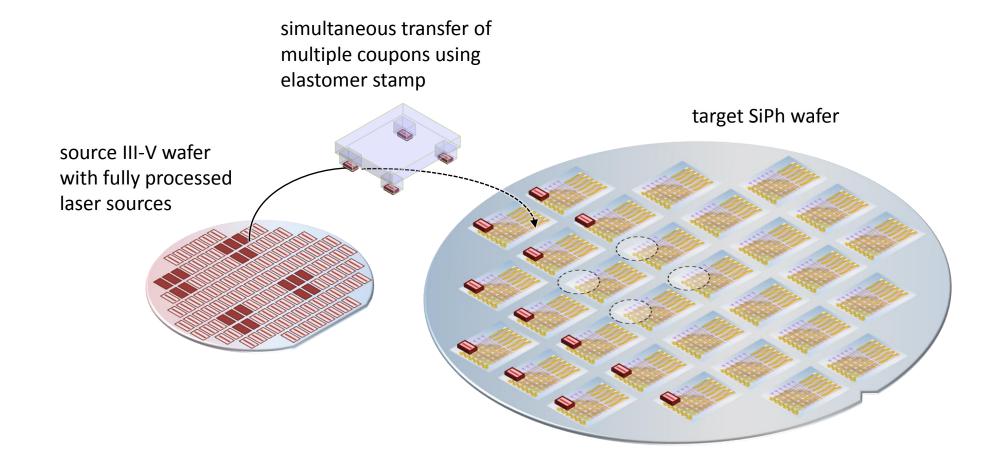

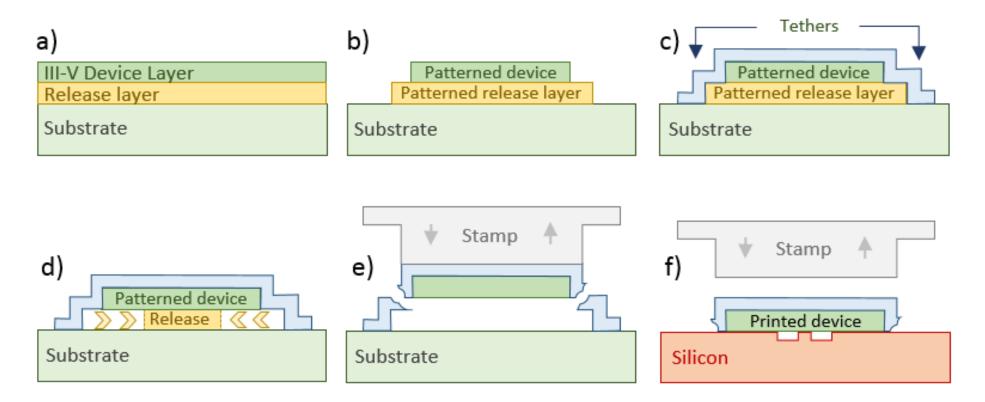

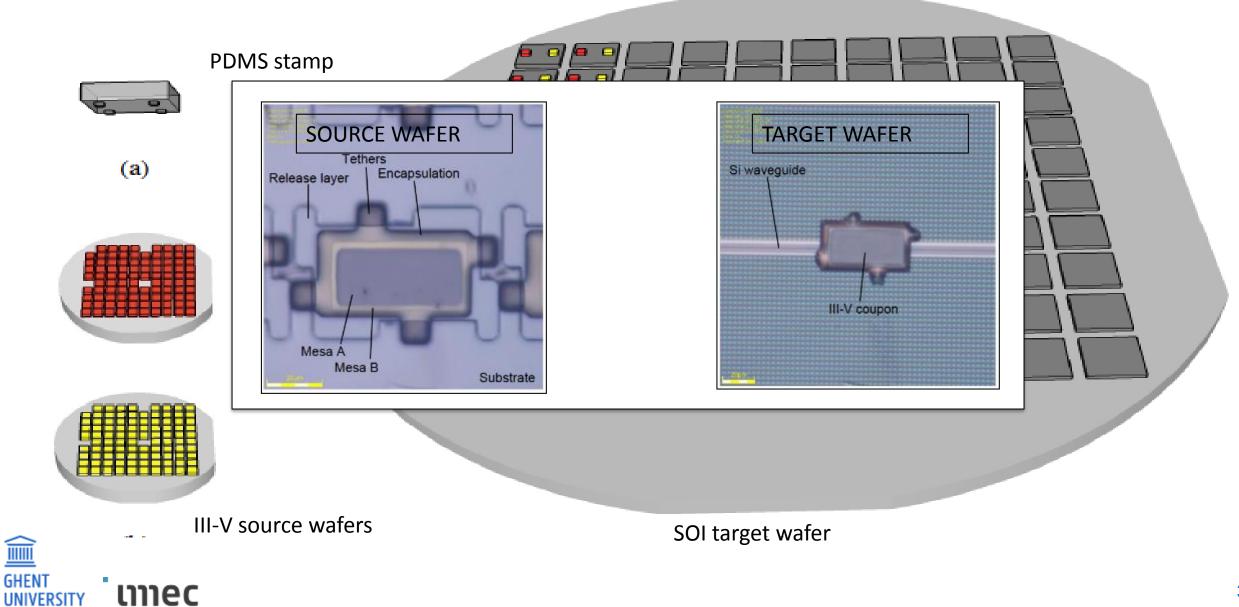

### MICRO-TRANSFER-PRINTING (µTP)

**IIII** GHENT

UNIVERSITY

unec

$\mu$ -TP combines advantages of flip-chip and die-to-wafer bonding

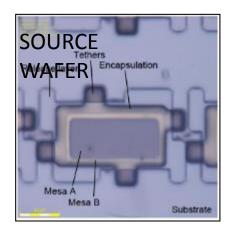

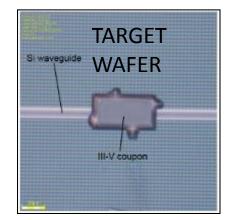

### **TRANSFER PRINTING**

<u>∭</u> GHENT

UNIVERSITY

unec

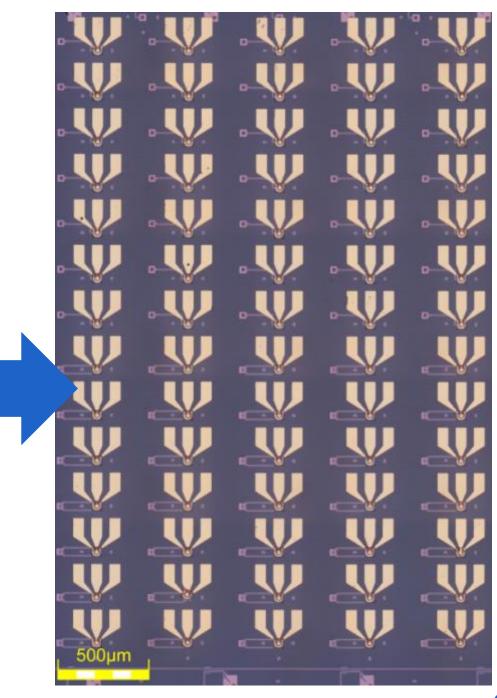

Transfer of micro-scale III-V coupons/devices to a Si target wafer

InP, GaAs, SOI, 2D materials, 0D materials

### TRANSFER PRINTING OF III-V SEMICONDUCTORS

UNIVERSITY

#### $\mu TP$ combines advantages of FLIP-CHIP and die-to-wafer bonding

#### **Massively parallel**

- >10,000 devices (LEDs) transferred per 45s cycle demonstrated

- Flip chip transfers individual devices.

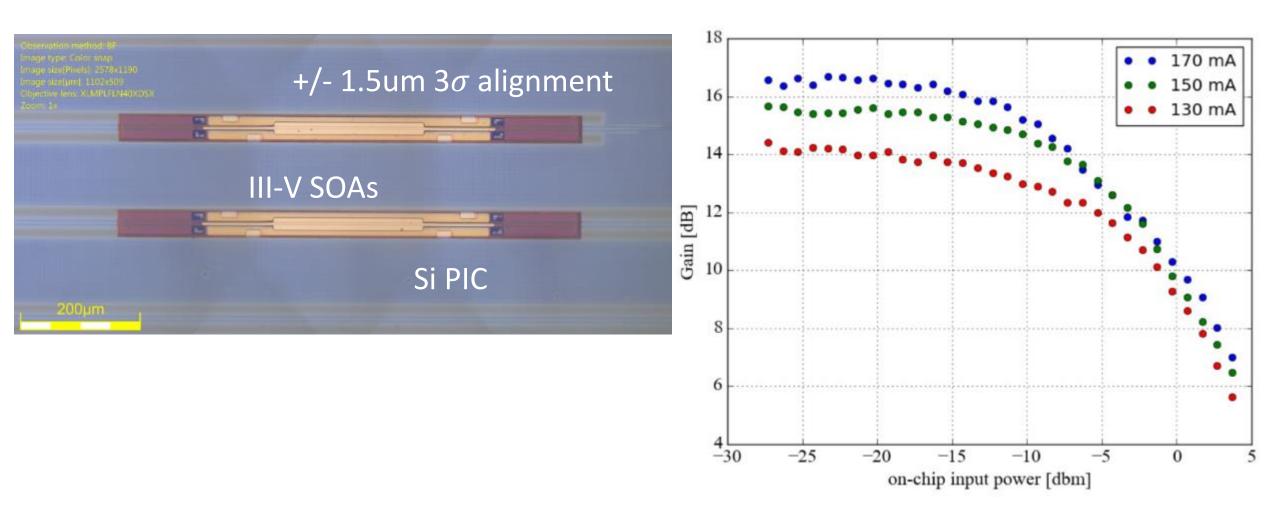

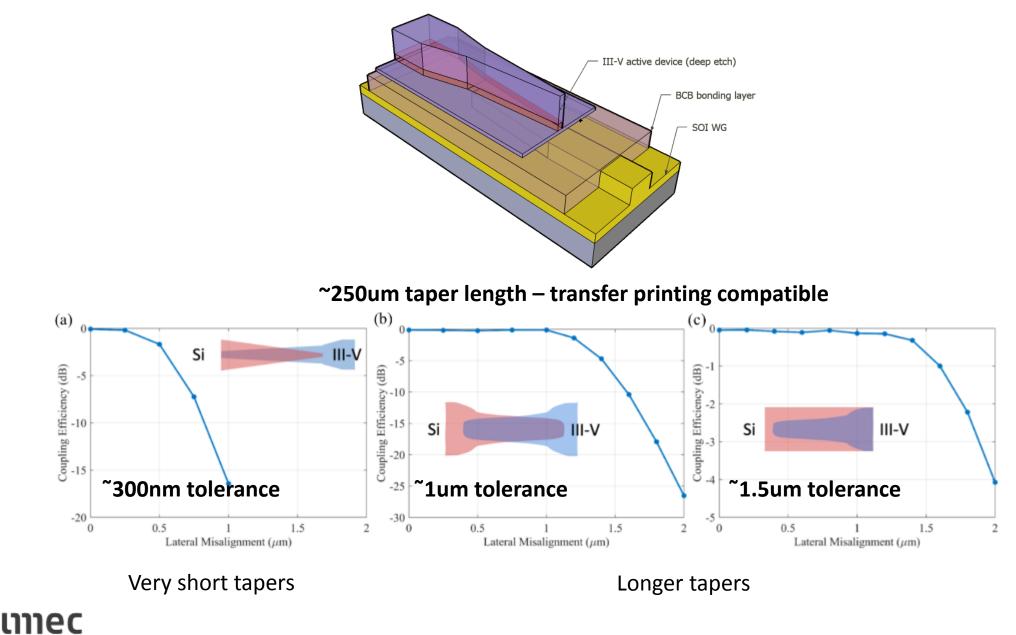

#### Position tolerance of ±1.5 $\mu$ m at 3 $\sigma$ in large arrays

- ±0.5µm and better when printed in small arrays

- Pattern recognition based

#### The highest quality source materials used

- Can be pre-processed

**GHEN1**

nec

#### Different types of devices or materials can be printed close to each other

#### Efficient use of expensive materials

- Width of devices << conventional for higher packing</li>

- Substrate can potentially be recovered

#### Independent of source substrate diameter

- InP wafers 50-100mm; Si wafers 200-300mm diameter

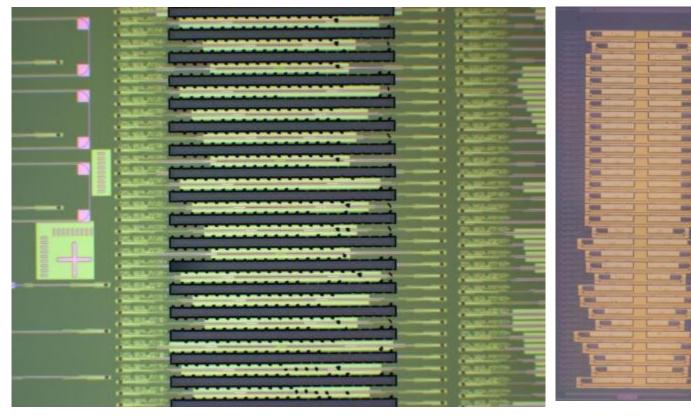

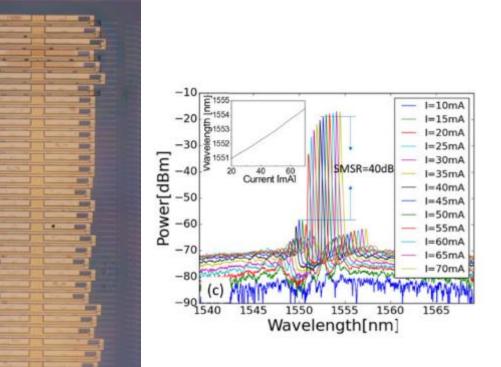

### FIRST III-V-ON-SILICON $\mu$ TP DFB LASERS

#### After transfer printing of coupons

#### Lasers after post-processing

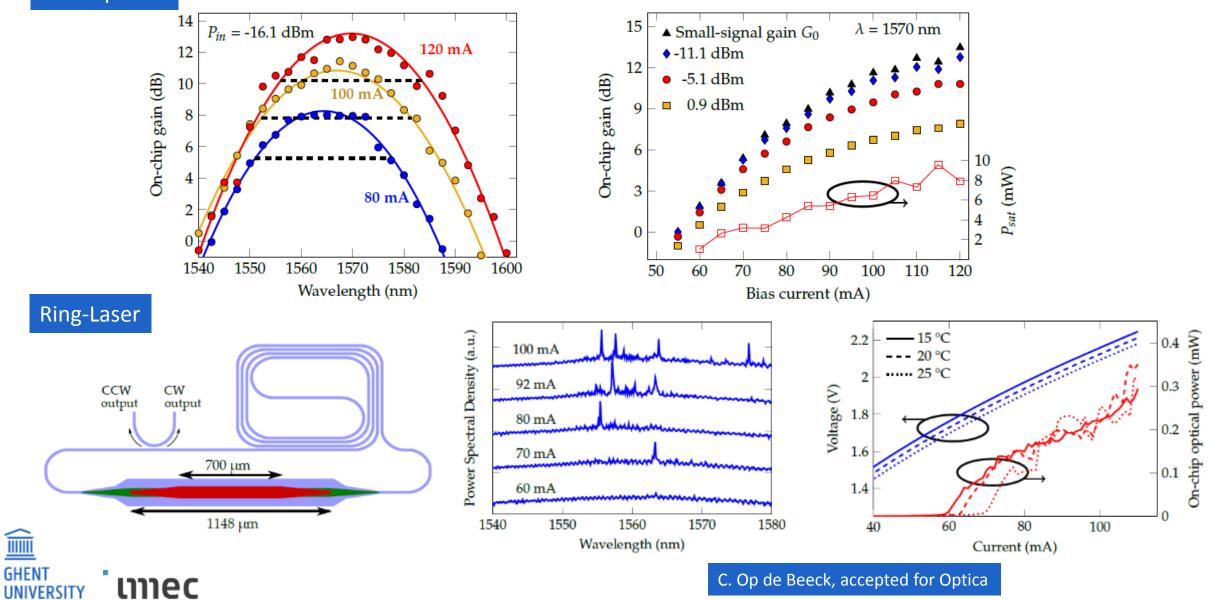

### TRANSFER PRINTED C-BAND SOAS

ALIGNMENT TOLERANT OPTICAL INTERFACE

**IIII** GHENT

UNIVERSITY

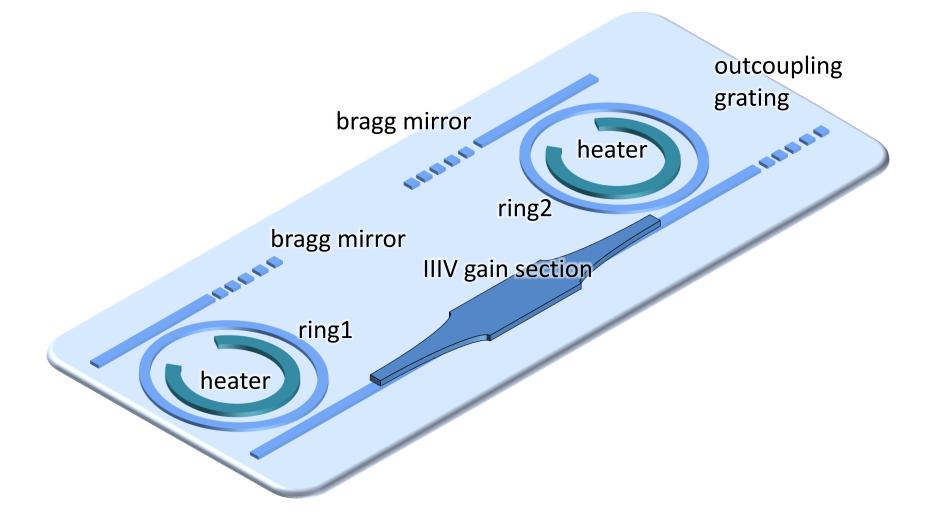

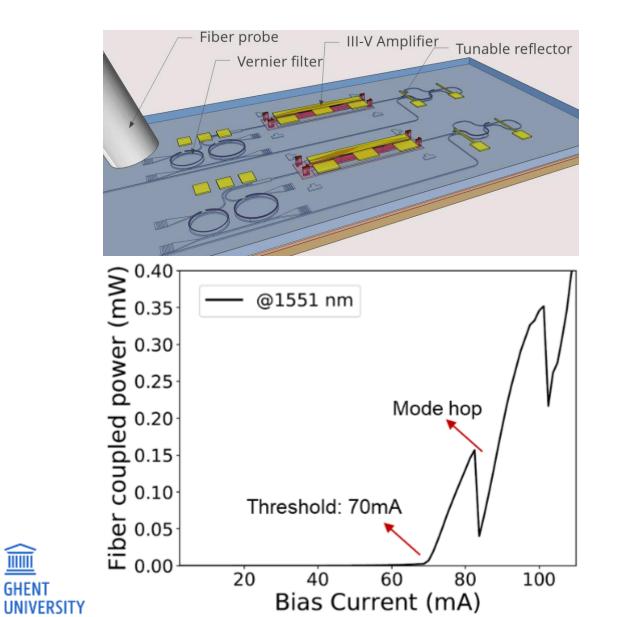

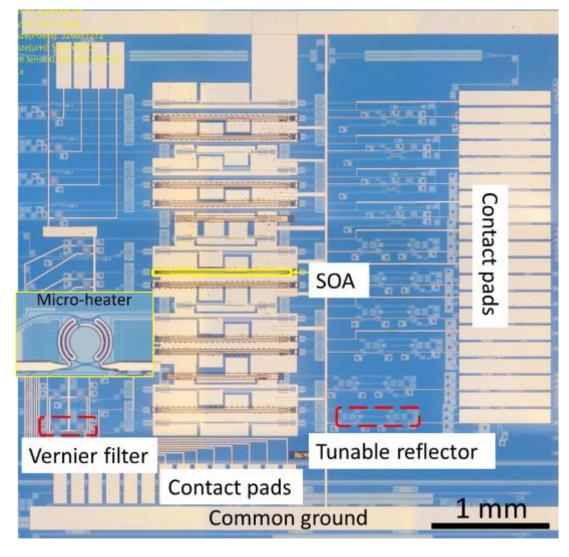

### III-V-ON-SI INTEGRATED WIDELY TUNABLE LASER

### **III-V-ON-SI INTEGRATED WIDELY TUNABLE LASER**

#### [J. Zhang et al., IEEE ECOC, 2019]

### III-V-ON-SI INTEGRATED WIDELY TUNABLE LASER

**IIII** GHENT

UNIVERSITY

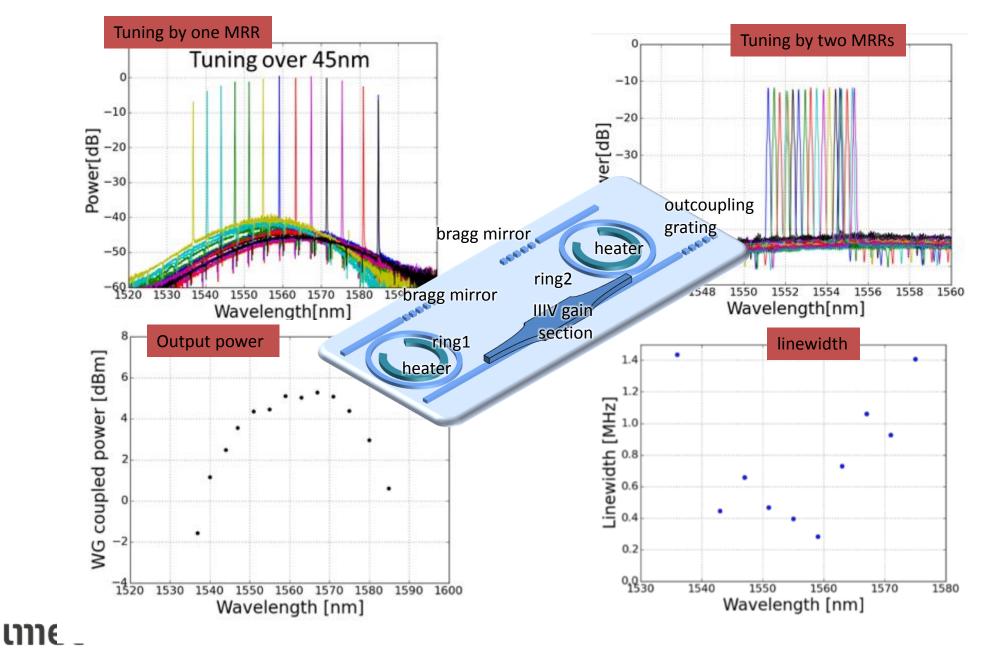

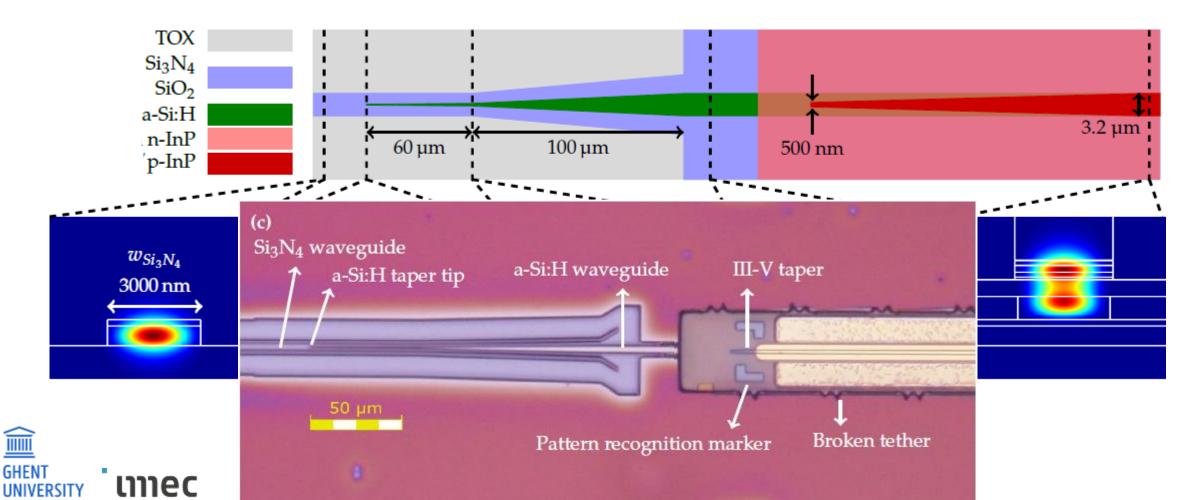

### INTEGRATION OF AMPLIFIERS AND LASERS ON SILICON NITRIDE

- Why: low loss, broader wavelength range

- Non-trivial given large index mismatch between InP and SiN

- Solution: intermediate amorphous silicon layer layer

### INTEGRATION OF AMPLIFIERS AND LASERS ON SILICON NITRIDE

On-chip Gain

### PRINTING ARRAYS OF C-BAND PDS

83/84 successful prints Good device uniformity

### CALADAN: INTEGRATION ON FULL PLATFORM

Heterogeneous integration is key to enabling new functionalities in silicon photonics

Broad diversity of heterogeneous material combinations and technologies in research

Adding heterogeneous integration to a complete process flow is non-trivial

Micro-transfer-printing has high potential in view of its agility and combination of "best-in-class" technologies

### 5<sup>TH</sup> EPIXFAB SILICON PHOTONIC SUMMER SCHOOL GHENT UNIVERSITY (BELGIUM)

#### DATE : 15 – 19 June 2020

#### **KEY FEATURES**

- Learn all about silicon photonics: from technology to applications

- Geared towards industrial and academic participants

- A perfect blend of learning and networking

#### **MORE INFO:**

e-mail: <u>info@ePIXfab.eu</u> web: <u>https://epixfab.eu/trainings/upcoming-trainings</u>

#### 4<sup>th</sup> ePIXfab Silicon Photonic Design Course

#### DATE : 8 – 12 June 2020

#### **KEY FEATURES**

unec

FRSITY

- 5 days hands-on silicon photonics design

- Layout, circuit simulation, design rules,

- Have your design fabricated and measured

: Promoting silicon photonics science, technology, and applications

#### **PHOTONICS RESEARCH GROUP**

#### **Roel Baets**

- E roel.baets@ugent.be

- T +32 496 559975

@PhotonicsUGent

www.photonics.intec.ugent.be